# 2.5 V/3.3 V Any Level Positive Input to -2.5 V/-3.3 V LVNECL Output Translator

#### Description

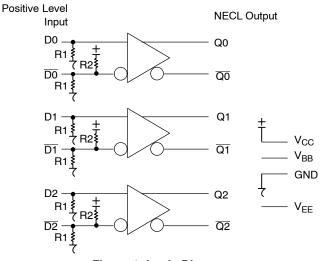

The NB100LVEP91 is a triple any level positive input to NECL output translator. The device accepts LVPECL, LVTTL, LVCMOS, HSTL, CML or LVDS signals, and translates them to differential LVNECL output signals (-2.5 V/-3.3 V).

To accomplish the level translation the LVEP91 requires three power rails. The  $V_{CC}$  pins should be connected to the positive power supply, and the  $V_{EE}$  pin should be connected to the negative power supply. The GND pins are connected to the system ground plane. Both  $V_{EE}$  and  $V_{CC}$  should be bypassed to ground via 0.01 µF capacitors.

Under open input conditions, the  $\overline{D}$  input will be biased at V<sub>CC</sub>/2 and the D input will be pulled to GND. These conditions will force the Q outputs to a low state, and Q outputs to a high state, which will ensure stability.

The V<sub>BB</sub> pin, an internally generated voltage supply, is available to this device only. For single-ended input conditions, the unused differential input is connected to V<sub>BB</sub> as a switching reference voltage. V<sub>BB</sub> may also rebias AC coupled inputs. When used, decouple V<sub>BB</sub> and V<sub>CC</sub> via a 0.01  $\mu$ F capacitor and limit current sourcing or sinking to 0.5 mA. When not used, V<sub>BB</sub> should be left open.

#### Features

- Maximum Input Clock Frequency > 2.0 GHz Typical

- Maximum Input Data Rate > 2.0 Gb/s Typical

- 500 ps Typical Propagation Delay

- Operating Range: V<sub>CC</sub> = 2.375 V to 3.8 V; V<sub>EE</sub> = -2.375 V to -3.8 V; GND = 0 V

- Q Output will Default LOW with Inputs Open or at GND

- Pb-Free Packages are Available\*

| А      | = Assembly Location |

|--------|---------------------|

| WL, L  | = Wafer Lot         |

| YY, Y  | = Year              |

| WW, W  | = Work Week         |

| G or ∎ | = Pb-Free Package   |

|        |                     |

(Note: Microdot may be in either location) \*For additional marking information, refer to Application Note AND8002/D.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 8 of this data sheet.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

Figure 1. Logic Diagram

#### Table 1. PIN DESCRIPTION

| F        | Pin               |                 |                                                   | Default |                                                                                                                                                                                 |

|----------|-------------------|-----------------|---------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOIC     | QFN               | Name            | I/O                                               | State   | Description                                                                                                                                                                     |

| 1, 20    | 3, 4, 12          | V <sub>CC</sub> | -                                                 | _       | Positive Supply Voltage. All V <sub>CC</sub> Pins must be Externally<br>Connected to Power Supply to Guarantee Proper Opera-<br>tion.                                           |

| 10       | 15, 16            | V <sub>EE</sub> | -                                                 | -       | Negative Supply Voltage. All V <sub>EE</sub> Pins must be Externally<br>Connected to Power Supply to Guarantee Proper Opera-<br>tion.                                           |

| 14, 17   | 19, 20, 23,<br>24 | GND             | -                                                 | -       | Ground.                                                                                                                                                                         |

| 4, 7     | 7, 11             | V <sub>BB</sub> | -                                                 | _       | ECL Reference Voltage Output                                                                                                                                                    |

| 2, 5, 8  | 5, 8, 13          | D[0:2]          | LVPECL, LVDS, LVTTL,<br>LVCMOS, CML, HSTL Input   | Low     | Noninverted Differential Inputs [0:2]. Internal 75 $k\Omega$ to GND.                                                                                                            |

| 3, 6, 9  | 6, 9, 14          | D[0:2]          | LVPECL, LVDS,<br>LVTTL,LVCMOS, CML,<br>HSTL Input | High    | Inverted Differential Inputs [0:2]. Internal 75 k $\Omega$ to GND and 75 k $\Omega$ to V <sub>CC</sub> . When Inputs are Left Open They Default to (V <sub>CC</sub> – GND) / 2. |

| 19,16,13 | 2, 22, 18         | Q[0:2]          | LVNECL Output                                     | -       | Noninverted Differential Outputs [0:2]. Typically Terminated with 50 $\Omega$ to V_{TT} = V_{CC} – 2 V                                                                          |

| 18,15,12 | 1, 21, 17         | Q[0:2]          | LVNECL Output                                     | -       | Inverted Differential Outputs [0:2]. Typically Terminated with 50 $\Omega$ to V_{TT} = V_CC – 2 V                                                                               |

| 11       | 10                | NC              | _                                                 | -       | No Connect. The NC Pin is NOT Electrically Connected to the Die and may Safely be Connected to Any Voltage from $V_{\rm EE}$ to $V_{\rm CC}.$                                   |

| N/A      | _                 | EP              | -                                                 |         | Exposed Pad. (Note 1)                                                                                                                                                           |

The thermally conductive exposed pad on the package bottom (see case drawing) must be attached to a heat sinking conduit and may only be electrically connected to V<sub>EE</sub> (not GND).

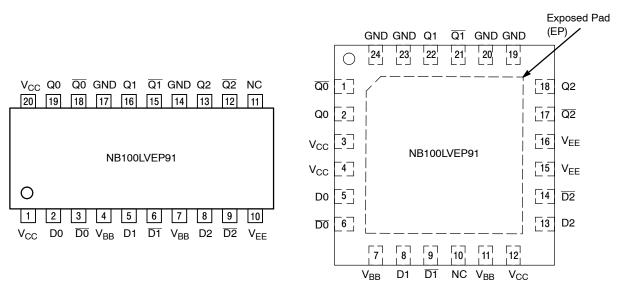

#### Figure 2. SOIC-20 Lead Pinout (Top View)\*

\*All  $V_{CC},\,V_{EE}$  and GND pins must be externally connected to a power supply.

Figure 3. QFN-24 Lead Pinout (Top View)\*

\*All V<sub>CC</sub>, V<sub>EE</sub> and GND pins must be externally connected to a power supply. The thermally conductive exposed pad on the package bottom (see case drawing) must be attached to a sufficient heat–sinking conduit and may only be electronically connected to V<sub>EE</sub> (not GND).

| Characteris                      | tics                                                      | Va                 | lue                  |

|----------------------------------|-----------------------------------------------------------|--------------------|----------------------|

| Internal Input Pulldown Resistor | (R1)                                                      | 75                 | kΩ                   |

| Internal Input Pullup Resistor   | (R2)                                                      | 75                 | kΩ                   |

| ESD Protection                   | Human Body Model<br>Machine Model<br>Charged Device Model | > 1                | 2 kV<br>50 V<br>2 kV |

| Moisture Sensitivity (Note 2)    |                                                           | Pb Pkg             | Pb-Free Pkg          |

|                                  | SO-20 WB<br>QFN-24                                        | Level 1<br>Level 1 | Level 3<br>Level 1   |

| Flammability Rating              | Oxygen Index: 28 to 34                                    | UL 94 V-0          | @ 0.125 in           |

| Transistor Count                 |                                                           | 446 D              | evices               |

| Meets or exceeds JEDEC Spec EIA/ | JESD78 IC Latchup Test                                    |                    |                      |

#### **Table 2. ATTRIBUTES**

2. For additional information, see Application Note AND8003/D.

#### **Table 3. MAXIMUM RATINGS**

| Symbol               | Parameter                                                                                                   | Condition 1         | Condition 2           | Rating         | Unit         |

|----------------------|-------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|----------------|--------------|

| V <sub>CC</sub>      | Positive Power Supply                                                                                       | GND = 0 V           |                       | 3.8 to 0       | V            |

| $V_{EE}$             | Negative Power Supply                                                                                       | GND = 0 V           |                       | –3.8 to 0      | V            |

| VI                   | Positive Input Voltage                                                                                      | GND = 0 V           | $V_{I}\!\leq\!V_{CC}$ | 3.8 to 0       | V            |

| V <sub>OP</sub>      | Operating Voltage                                                                                           | GND = 0 V           | $V_{CC} - V_{EE}$     | 7.6 to 0       | V            |

| l <sub>out</sub>     | Output Current                                                                                              | Continuous<br>Surge |                       | 50<br>100      | mA<br>mA     |

| I <sub>BB</sub>      | PECL V <sub>BB</sub> Sink/Source                                                                            |                     |                       | ± 0.5          | mA           |

| T <sub>A</sub>       | Operating Temperature Range                                                                                 |                     |                       | -40 to +85     | °C           |

| T <sub>stg</sub>     | Storage Temperature Range                                                                                   |                     |                       | –65 to +150    | °C           |

| $\theta_{JA}$        | Thermal Resistance (Junction-to-Ambient)<br>JESD 51-3 (1S-Single Layer Test Board)                          | 0 lfpm<br>500 lfpm  | SOIC-20<br>SOIC-20    | 90<br>60       | °C/W<br>°C/W |

| $\theta_{JA}$        | Thermal Resistance (Junction-to-Ambient)<br>JESD 51-6 (2S2P Multilayer Test Board) with Filled Thermal Vias | 0 lfpm<br>500 lfpm  | QFN-24<br>QFN-24      | 37<br>32       | °C/W<br>°C/W |

| $\theta_{\text{JC}}$ | Thermal Resistance (Junction-to-Case)                                                                       | Standard Board      | SOIC-20<br>QFN-24     | 30 to 35<br>11 | °C/W<br>°C/W |

| T <sub>sol</sub>     | Wave Solder Pb<br>Pb-Free                                                                                   |                     |                       | 225<br>225     | °C           |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

## Table 4. DC CHARACTERISTICS POSITIVE INPUTS V<sub>CC</sub> = 2.5 V, V<sub>EE</sub> = -2.375 to -3.8 V, GND = 0 V (Note 3)

|                 |                                                                               |   | -           | 40°C |                 | :           | 25°C |          |             | 85°C |          |      |

|-----------------|-------------------------------------------------------------------------------|---|-------------|------|-----------------|-------------|------|----------|-------------|------|----------|------|

| Symbol          | Characteristic                                                                | I | Min         | Тур  | Max             | Min         | Тур  | Max      | Min         | Тур  | Max      | Unit |

| I <sub>CC</sub> | Positive Power Supply Current                                                 |   | 10          | 14   | 20              | 10          | 14   | 20       | 10          | 14   | 20       | mA   |

| VIH             | Input HIGH Voltage (Single-Ended)                                             | 1 | 335         |      | $V_{\text{CC}}$ | 1335        |      | $V_{CC}$ | 1335        |      | $V_{CC}$ | mV   |

| VIL             | Input LOW Voltage (Single-Ended)                                              | G | GND         |      | 875             | GND         |      | 875      | GND         |      | 875      | mV   |

| VIHCMR          | Input HIGH Voltage Common Mode Range<br>(Differential Configuration) (Note 4) |   | 0           |      | 2.5             | 0           |      | 2.5      | 0           |      | 2.5      | V    |

| I <sub>IH</sub> | Input HIGH Current (@ V <sub>IH</sub> )                                       |   |             |      | 150             |             |      | 150      |             |      | 150      | μΑ   |

| Ι <sub>ΙL</sub> | Input LOW Current (@ V <sub>IL</sub> )                                        |   | 0.5<br>-150 |      |                 | 0.5<br>-150 |      |          | 0.5<br>-150 |      |          | μΑ   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

3. Input parameters vary 1:1 with V<sub>CC</sub>. V<sub>CC</sub> can vary +1.3 V / -0.125 V. 4. V<sub>IHCMR</sub> min varies 1:1 with GND. V<sub>IHCMR</sub> max varies 1:1 with V<sub>CC</sub>.

|                 |                                                                               |             |       |                 |             |      |                 | -           |      |                 |      |

|-----------------|-------------------------------------------------------------------------------|-------------|-------|-----------------|-------------|------|-----------------|-------------|------|-----------------|------|

|                 |                                                                               |             | –40°C |                 | 25°C        |      |                 | 85°C        |      |                 |      |

| Symbol          | Characteristic                                                                | Min         | Тур   | Max             | Min         | Тур  | Max             | Min         | Тур  | Max             | Unit |

| I <sub>CC</sub> | Positive Power Supply Current                                                 | 10          | 16    | 24              | 10          | 16   | 24              | 10          | 16   | 24              | mA   |

| $V_{\text{IH}}$ | Input HIGH Voltage (Single-Ended)                                             | 2135        |       | V <sub>CC</sub> | 2135        |      | V <sub>CC</sub> | 2135        |      | V <sub>CC</sub> | mV   |

| VIL             | Input LOW Voltage (Single-Ended)                                              | GND         |       | 1675            | GND         |      | 1675            | GND         |      | 1675            | mV   |

| $V_{BB}$        | PECL Output Voltage Reference                                                 | 1775        | 1875  | 1975            | 1775        | 1875 | 1975            | 1775        | 1875 | 1975            | mV   |

| VIHCMR          | Input HIGH Voltage Common Mode Range<br>(Differential Configuration) (Note 6) | 0           |       | 3.3             | 0           |      | 3.3             | 0           |      | 3.3             | V    |

| I <sub>IH</sub> | Input HIGH Current (@ V <sub>IH</sub> )                                       |             |       | 150             |             |      | 150             |             |      | 150             | μA   |

| IIL             | Input LOW Current (@ V <sub>IL</sub> ) D<br>D                                 | 0.5<br>-150 |       |                 | 0.5<br>-150 |      |                 | 0.5<br>-150 |      |                 | μΑ   |

#### Table 5. DC CHARACTERISTICS POSITIVE INPUT $V_{CC}$ = 3.3 V; $V_{EE}$ = -2.375 V to -3.8 V; GND = 0 V (Note 5)

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

5. Input parameters vary 1:1 with  $V_{CC}$ .  $V_{CC}$  can vary +0.5 / -0.925 V.

6.  $V_{IHCMR}$  min varies 1:1 with GND.  $V_{IHCMR}$  max varies 1:1 with  $V_{CC}$ .

#### Table 6. DC CHARACTERISTICS NECL OUTPUT $V_{CC} = 2.375$ V to 3.8 V; $V_{EE} = -2.375$ V to -3.8 V; GND = 0 V (Note 7)

|                 |                               | -40°C |       |       | 25°C  |       |       |       |       |       |      |

|-----------------|-------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol          | Characteristic                | Min   | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Unit |

| I <sub>EE</sub> | Negative Power Supply Current | 40    | 50    | 60    | 38    | 50    | 68    | 38    | 50    | 68    | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 8)  | -1145 | -1020 | -895  | -1145 | -1020 | -895  | -1145 | -1020 | -895  | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 8)   | -1945 | -1770 | -1600 | -1945 | -1770 | -1600 | -1945 | -1770 | -1600 | mV   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

7. Output parameters vary 1:1 with GND.

8. All loading with 50  $\Omega$  resistor to GND – 2.0 V.

|                                       |                                                                                     |                                                                                                                                |                   | –40°C             |                 |                   | 25°C              |                  |                   | 85°C              |                  |      |

|---------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-----------------|-------------------|-------------------|------------------|-------------------|-------------------|------------------|------|

| Symbol                                | Characteristic                                                                      |                                                                                                                                | Min               | Тур               | Max             | Min               | Тур               | Max              | Min               | Тур               | Max              | Unit |

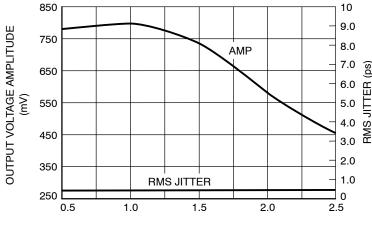

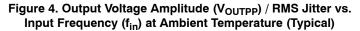

| V <sub>OUTPP</sub>                    | Output Voltage Amplitude<br>(Figure 4)<br>(Note 9)                                  | $\begin{array}{l} f_{in} \leq 1.0 \; \text{GHz} \\ f_{in} \leq 1.5 \; \text{GHz} \\ f_{in} \leq 2.0 \; \text{GHz} \end{array}$ | 575<br>525<br>300 | 800<br>750<br>600 |                 | 600<br>525<br>250 | 800<br>750<br>550 |                  | 550<br>400<br>150 | 800<br>750<br>500 |                  | mV   |

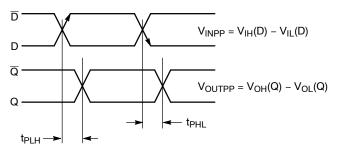

| t <sub>PLH</sub><br>t <sub>PHL0</sub> | Propagation Delay<br>D to Q                                                         | Differential<br>Single-Ended                                                                                                   | 375<br>300        | 500<br>450        | 600<br>650      | 375<br>300        | 500<br>450        | 600<br>675       | 400<br>300        | 550<br>500        | 650<br>750       | ps   |

| t <sub>SKEW</sub>                     | Pulse Skew (Note 10)<br>Output-to-Output (Note 11)<br>Part-to-Part (Diff) (Note 11) |                                                                                                                                |                   | 15<br>25<br>50    | 75<br>95<br>125 |                   | 15<br>30<br>50    | 75<br>105<br>125 |                   | 15<br>30<br>70    | 80<br>105<br>150 | ps   |

| t <sub>JITTER</sub>                   | RMS Random Clock Jitter (Note 12<br>Peak-to-Peak Data Dependant Jitt<br>(Note 13)   |                                                                                                                                |                   | 0.5<br>20         | 2.0             |                   | 0.5<br>20         | 2.0              |                   | 0.5<br>20         | 2.0              | ps   |

| V <sub>INPP</sub>                     | Input Voltage Swing (Differential Co<br>(Note 14)                                   | onfiguration)                                                                                                                  | 200               | 800               | 1200            | 200               | 800               | 1200             | 200               | 800               | 1200             | mV   |

| t <sub>r</sub> , t <sub>f</sub>       | Output Rise/Fall Times @ 50 MHz<br>(20% - 80%)                                      | Q, <u>Q</u>                                                                                                                    | 75                | 150               | 250             | 75                | 150               | 250              | 75                | 150               | 275              | ps   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

9. Measured using a 750 mV source, 50% duty cycle clock source. All loading with 50 Ω to GND - 2.0 V. Input edge rates 150 ps (20% - 80%). 10. Pulse Skew =  $|\bar{t}_{PLH} - t_{PHL}|$

11. Skews are valid across specified voltage range, part-to-part skew is for a given temperature.

12. RMS Jitter with 50% Duty Cycle Input Clock Signal. 13. Peak-to-Peak Jitter with input NRZ PRBS 2<sup>31-1</sup> at 2.0 Gb/s.

14. Input voltage swing is a single-ended measurement operating in differential mode. The device has a DC gain of ~ 50.

Figure 5. AC Reference Measurement

### **Application Information**

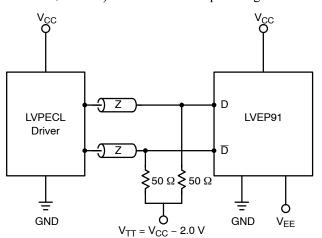

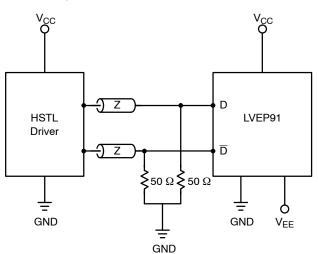

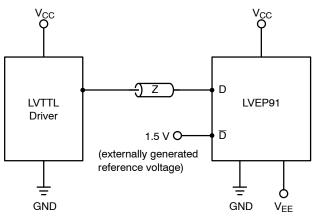

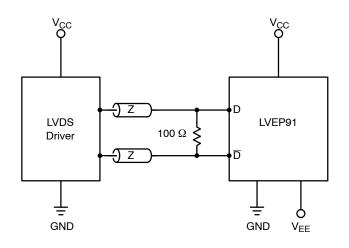

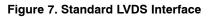

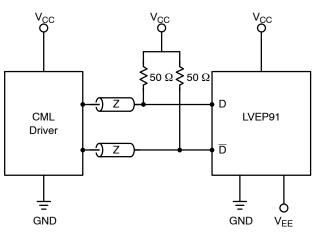

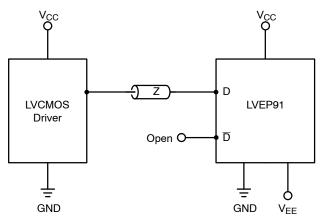

All NB100LVEP91 inputs can accept LVPECL, LVTTL, LVCMOS, HSTL, CML, or LVDS signal levels. The limitations for differential input signal (LVDS, HSTL, LVPECL, or CML) are the minimum input swing of 150 mV

Figure 6. Standard LVPECL Interface

Figure 8. Standard HSTL Interface

Figure 10. Standard LVTTL Interface

and the maximum input swing of 3.0 V. Within these conditions, the input voltage can range from  $V_{CC}$  to GND. Examples interfaces are illustrated below in a 50  $\Omega$  environment (Z = 50  $\Omega$ )

#### Figure 9. Standard 50 $\Omega$ Load CML Interface

Figure 11. Standard LVCMOS Interface (D will default to  $V_{CC}/2$  when left open. A reference voltage of  $V_{CC}/2$  should be applied to D input, if  $\overline{D}$  is interfaced to CMOS signals.)

#### **ORDERING INFORMATION**

| Device           | Package             | Shipping <sup>†</sup> |

|------------------|---------------------|-----------------------|

| NB100LVEP91DW    | SO-20               | 38 Units / Rail       |

| NB100LVEP91DWG   | SO–20<br>(Pb–Free)  | 38 Units / Rail       |

| NB100LVEP91DWR2  | SO-20               | 1000 / Tape & Reel    |

| NB100LVEP91DWR2G | SO–20<br>(Pb–Free)  | 1000 / Tape & Reel    |

| NB100LVEP91MN    | QFN-24              | 92 Units / Rail       |

| NB100LVEP91MNG   | QFN-24<br>(Pb-Free) | 92 Units / Rail       |

| NB100LVEP91MNR2  | QFN-24              | 3000 / Tape & Reel    |

| NB100LVEP91MNR2G | QFN-24<br>(Pb-Free) | 3000 / Tape & Reel    |

+ For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

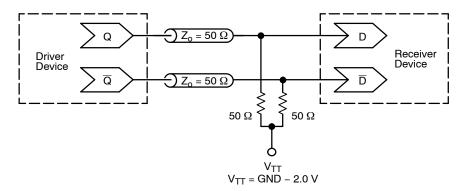

Figure 12. Typical Termination for Output Driver and Device Evaluation (See Application Note AND8020/D – Termination of ECL Logic Devices.)

#### **Resource Reference of Application Notes**

| AN1405/D  | - | ECL Clock Distribution Techniques           |

|-----------|---|---------------------------------------------|

| AN1406/D  | - | Designing with PECL (ECL at +5.0 V)         |

| AN1503/D  | _ | ECLinPS <sup>™</sup> I/O SPiCE Modeling Kit |

| AN1504/D  | _ | Metastability and the ECLinPS Family        |

| AN1568/D  | _ | Interfacing Between LVDS and ECL            |

| AN1672/D  | _ | The ECL Translator Guide                    |

| AND8001/D | _ | Odd Number Counters Design                  |

| AND8002/D | - | Marking and Date Codes                      |

| AND8020/D | _ | Termination of ECL Logic Devices            |

| AND8066/D | - | Interfacing with ECLinPS                    |

| AND8090/D | _ | AC Characteristics of ECL Devices           |

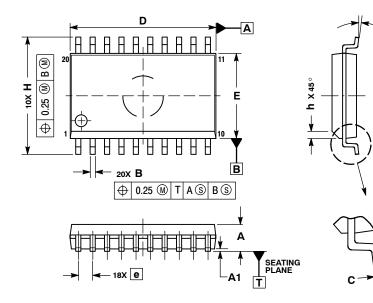

### PACKAGE DIMENSIONS

SO-20 WB CASE 751D-05 ISSUE G

6

- NOTES:

DIMENSIONS ARE IN MILLIMETERS.

INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS |

|-----|--------|--------|

| DIM | MIN    | MAX    |

| Α   | 2.35   | 2.65   |

| A1  | 0.10   | 0.25   |

| В   | 0.35   | 0.49   |

| С   | 0.23   | 0.32   |

| D   | 12.65  | 12.95  |

| Е   | 7.40   | 7.60   |

| e   | 1.27   | BSC    |

| Η   | 10.05  | 10.55  |

| h   | 0.25   | 0.75   |

| L   | 0.50   | 0.90   |

| θ   | 0 °    | 7 °    |

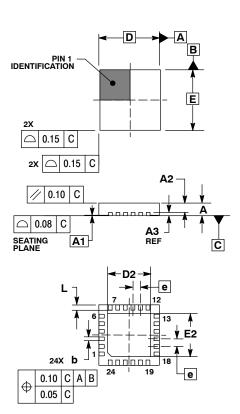

#### PACKAGE DIMENSIONS

QFN 24 MN SUFFIX 24 PIN QFN, 4x4 CASE 485L-01 ISSUE O

NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL.

- FROM TERMINAL. 4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |      |

|-----|-------------|------|

| DIM | MIN         | MAX  |

| Α   | 0.80        | 1.00 |

| A1  | 0.00        | 0.05 |

| A2  | 0.60        | 0.80 |

| A3  | 0.20 REF    |      |

| b   | 0.23        | 0.28 |

| D   | 4.00 BSC    |      |

| D2  | 2.70        | 2.90 |

| E   | 4.00 BSC    |      |

| E2  | 2.70        | 2.90 |

| е   | 0.50 BSC    |      |

| L   | 0.35        | 0.45 |

ECLinPS is a trademark of Semiconductor Components Industries, LLC.

ON Semiconductor and ()) are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application is intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized to subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative